## Модуль аналоговых интерфейсов для спутникового мультиплексора

B.B. Швагер

*Ростовский-на-Дону научно-исследовательский институт радиосвязи*

**Аннотация:** Представлена разработка модуля аналоговых интерфейсов для спутникового мультиплексора, с возможностью встраивания в структуру группового сигнала со скоростями ниже 16 кбит/с и обеспечивающего взаимодействие с широким набором абонентского телефонного оборудования по интерфейсам FXS, FXO, E&M.

**Ключевые слова:** передача речи, мультиплексор, канaloобразующая аппаратура, система спутниковой связи, модуль аналоговых интерфейсов, групповой сигнал, FXS, FXO, E&M.

Речь остается наиболее распространенной формой человеческого общения. Для удаленной эффективной связи акустические речевые сигналы при помощи кодеков преобразуются в цифровую форму с уменьшенной скоростью передачи данных при сохранении качества декодированной речи.

В настоящее время отечественные и зарубежные производители спутниковых мультиплексоров (Морион, Супертел, Zelax, Ubiquiti и др.), предлагают различные решения для передачи речевых сигналов. Часть производителей в своих решениях не сжимают голос, оставляя его на уровне импульсно-кодовой модуляции (64 кбит/с), другие используют кодеки, благодаря которым удается сжать цифровой поток в 4 и более раз. Несмотря на стремление повысить эффективность использования пропускной способности канала, ни одно решение не позволяет организовать речевой канал связи на низких скоростях (менее 16 кбит/с), ввиду использования стандартных протоколов VoIP связи.

Зарубежное и отечественное оборудование также функционирует по закрытым алгоритмам, поэтому модификация и расширение функциональных возможностей, а, следовательно, и применение таких модулей невозможна.

Таким образом, задача разработки модуля аналоговых интерфейсов на базе собственных алгоритмов для спутникового мультиплексора является актуальной.

### Цель работы.

Расширение функциональных возможностей мультиплексора в составе спутниковых станций. Обеспечение возможности сертификации модуля аналоговых интерфейсов.

Решаемые задачи:

- 1) Разработка электрической схемы и печатной платы модуля аналоговых интерфейсов;

- 2) Реализация абонентских интерфейсов и алгоритма их встраивания в структуру группового сигнала с временным разделением трафика на ПЛИС.

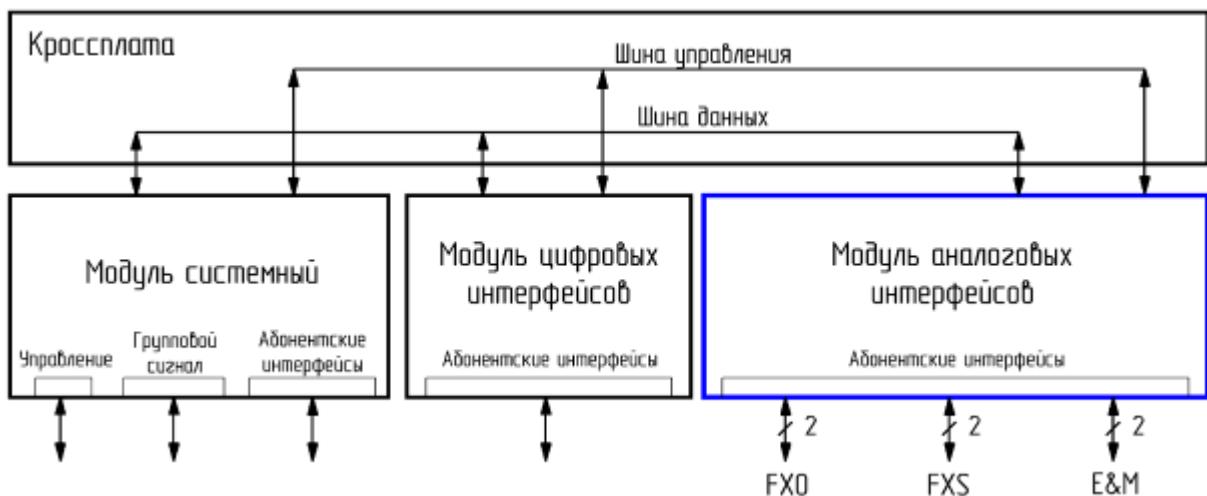

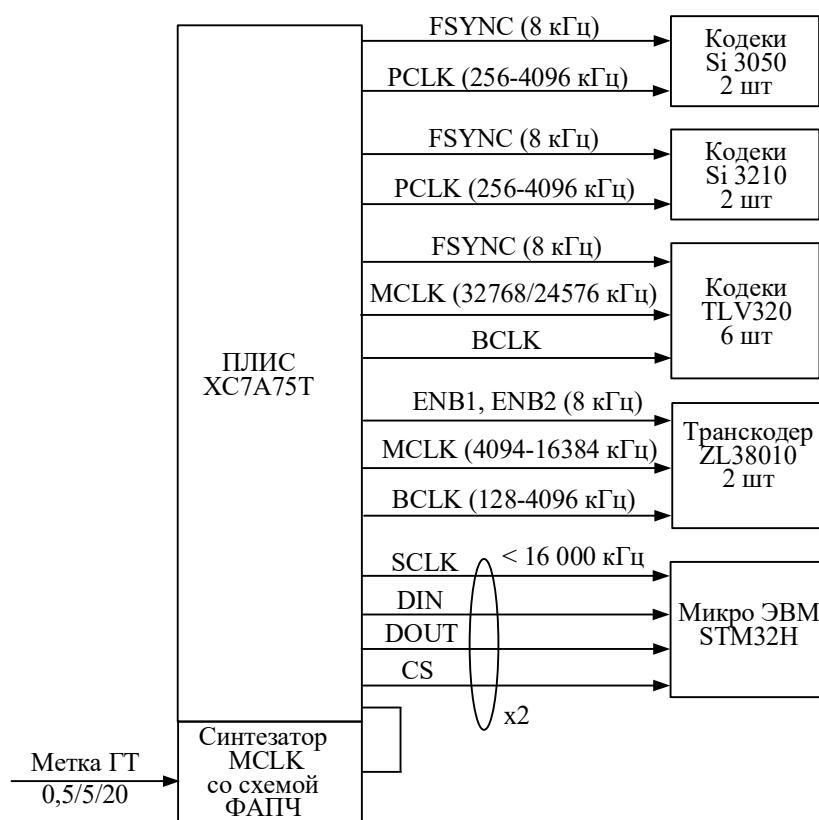

Для выполнения решаемых задач, техническая реализация модуля аналоговых интерфейсов производилась в соответствии с разработанной структурной схемой, приведенной на рис. 1, на основе взятого за прототип изобретения [1], патент RU 2690785.

Рисунок 1. - Структурная схема встраивания модуля аналоговых интерфейсов в спутниковый мультиплексор

Модуль аналоговых интерфейсов осуществляет взаимодействие с источниками аналоговых сигналов телефонии по интерфейсам FXO, FXS, E&M тип 5, разделение сигналов линейной сигнализации и трафика канала ТЧ и их преобразование для передачи через цифровой тракт радиоканала [2]. В модуле осуществляется преобразование аналоговых сигналов канала ТЧ по рекомендации G711 закон А (скорость 64 кбит/с), и далее при необходимости кодирование по рекомендациям G726, G728, МСЭ (скорости 32, 16 кбит/с), SPEEX (скорость 8 кбит/с). Данные выдаются на заданных позициях цикла выходного сигнала.

Проведенный в рамках решения первой задачи анализ доступной элементной базы [3,4] для реализации интерфейсов FXO, FXS, E&M показал, что в России выпускаются несколько типов микросхем только для реализации телефонных аппаратов (звонок, табло, номеронабиратель, схема разделения) и одноканальный кофидек, обеспечивающий преобразование аналогового сигнала и обратно по рекомендации G711 закон А. Реализация интерфейсов FXS, FXO на базе этих микросхем практически невозможна.

За рубежом специализированные БИС для проводной телефонной связи и интерфейсов FXS, FXO, E&M выпускаются множеством фирм, в том или ином объеме, причем в последнее время эти СБИС ориентированы на системы VoIP, мультисервисные системы [5], что сильно ограничивает возможность их использования в низкоскоростных режимах. По результатам проведенного анализа обнаружен производитель СБИС, явно указывающих на возможность реализации интерфейса FXO, а именно Silicon labs (Китай) с линейкой микросхем серии Si 3050, Si 3011/18/19, Si 3201, Si 3210.

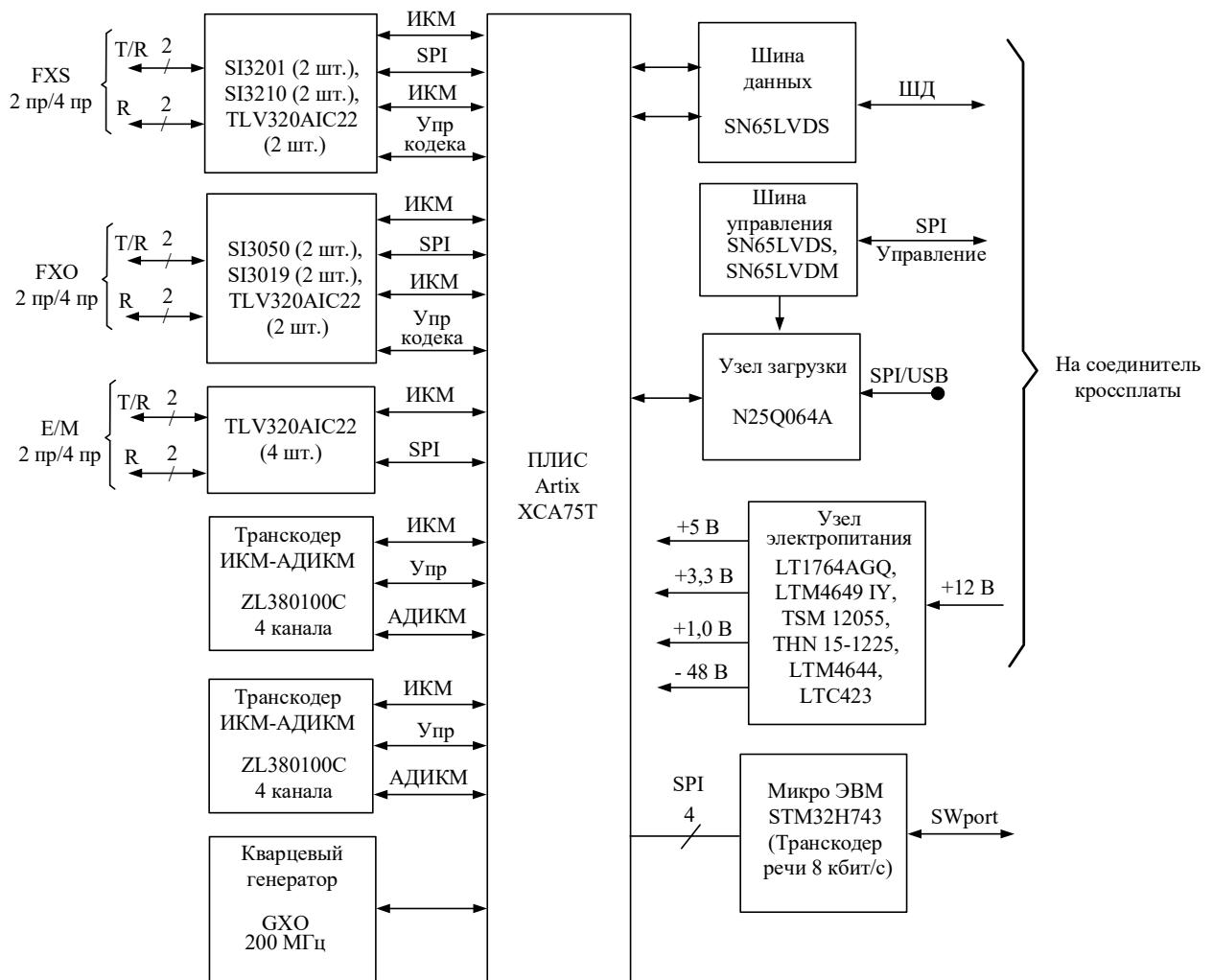

Рисунок 2. – Структурная схема модуля аналоговых интерфейсов

Рассмотрим разработанную структурную схему [6]. Двухканальный интерфейс FXO реализован на двух парах СБИС Si 3019 – Si 3050, обеспечивающих работу в 2-х проводном режиме и двух дополнительных СБИС кодеков TLV320AI22, обеспечивающих работу в 4-х проводном режиме, связь интерфейса с ПЛИС по интерфейсам ИКМ и SPI.

Интерфейс FXO при работе с двухпроводными или четырехпроводными абонентскими линиями обеспечивает:

- формирование для АТС сигнала занятия абонентской линии, формируемого удаленным интерфейсом FXS и передаваемого через цифровую линию, и передачу сигналов набора номера от FXS на АТС;

- прием сигналов вызова удаленного абонента от АТС и передача их на удаленный интерфейс FXS;

- аналого-цифровое преобразование и цифро-аналоговое преобразование передаваемого и принимаемого сигналов, объединение аналоговых сигналов передачи и приема в двухпроводную абонентскую линию;

- возможность регулировки уровней сигналов приема и передачи;

- передачу сигнализации в СУВ или информационном канале.

Двухканальный интерфейс FXS реализован на двух парах СБИС Si 3201 – Si 3210, предназначенных для работы в двухпроводном режиме. Для работы в 4-х проводном режиме используются дополнительные СБИС кодеков TLV320AI22, связь с ПЛИС по интерфейсам ИКМ и SPI.

Интерфейс FXS при работе с двухпроводными или четырехпроводными абонентскими линиями обеспечивает:

- подачу в линию напряжения питания 48В;

- обнаружение в линии занятия (снятия телефонной трубки) и передачу сигнала занятия в цифровой радиолинии через специальный канал СУВ или внутри разговорного канала;

- разделение сигнала двухпроводной линии на линии передачи и приема и подачу сигналов на кофидек;

- аналого-цифровое преобразование передаваемого сигнала и обратное преобразование сигнала, поступающего по цифровой радиолинии с регулировкой уровня звукового сигнала;

- формирование вызывного сигнала на ТА (звонка) при поступлении вызова от удаленной АТС по сигнализации цифровой радиолинии.

---

Двухканальный интерфейс E&M реализован на СБИС кодеков TLV320AI22 (4 шт.), трансформаторах для гальванической развязки и обеспечивает работу в двухпроводном и 4-х проводном режимах. Связь с ПЛИС по интерфейсам ИКМ и SPI.

Интерфейс E&M обеспечивает:

- передачу по 4-х проводным линиям абонентского трафика (полосы канала ТЧ) с гальваническим разделением цепей;

- аналого-цифровое преобразование и цифро-аналоговое преобразование передаваемого и принимаемого сигналов, объединение аналоговых сигналов передачи и приема в двухпроводную абонентскую линию;

- возможность регулировки уровней сигналов приема и передачи;

- передачу сигнализации в СУВ или информационном канале.

Транскодеры ИКМ – АДИКМ реализованы на двух ИМС ZL380100C, каждая из которых является четырехканальной. Итого две ИМС обеспечивают транскодирование сигналов ИКМ, формируемых всеми тремя интерфейсами FXS, FXO, E&M. Транскодеры преобразуют исходный код ИКМ со скоростью передачи 64 кбит/с в код АДИКМ одной из скоростей: 32, 24, 16 кбит/с.

Микро-ЭВМ STM32H743 используется для транскодирования сигналов ИКМ в канальные сигналы со скоростями передачи 8 кбит/с и ниже. Конкретные алгоритмы транскодирования загружаются во флэш-память микро-ЭВМ при настройке. Для алгоритма SPEEX – количество обрабатываемых дуплексных каналов равно двум. Связь микросхемы STM32H743 с ПЛИС через четыре интерфейса SPI.

Управление всем модулем осуществляется с помощью интерфейса SPI, на физическом уровне которого используется ИМС SN65LVDS, SN65LVDM.

---

Загрузка конфигурации ПЛИС Artix 7 XCA75T осуществляется из флэш-памяти N25Q064A после включения питания [7].

Электропитание модуля осуществляется напряжением +12В. В модуле это напряжение преобразуется в ряд вторичных напряжений питания, в том числе, в напряжение 48В, необходимое для цепей сигнализации интерфейсов Е&М. Модуль оборудован средствами для горячего замены модуля без отключения электропитания мультиплексора (используются специальные соединители и ИМС защиты цепи общего электропитания).

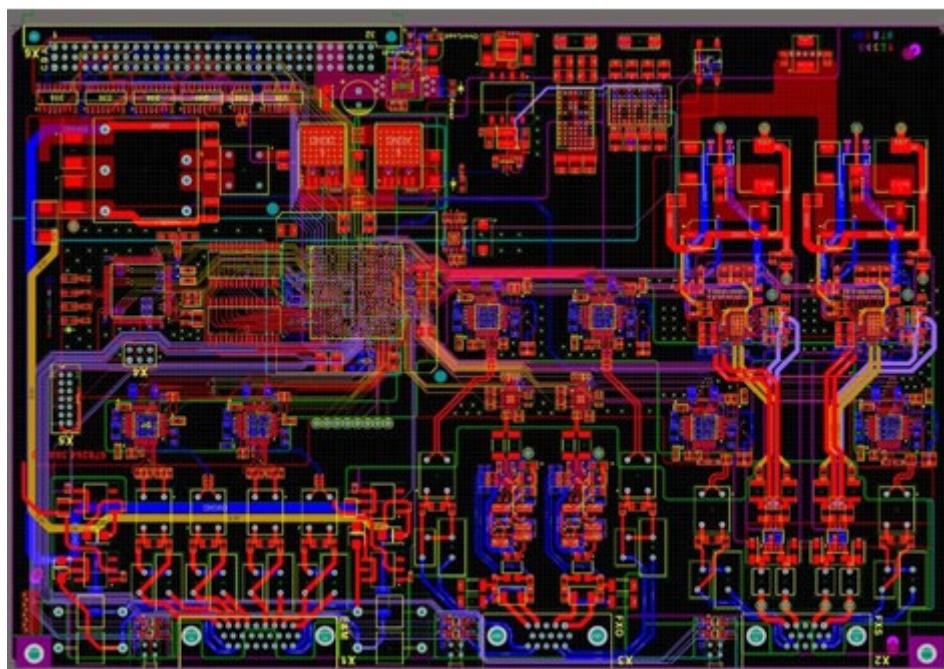

Модуль аналоговых интерфейсов выполнен в виде печатной платы стандарта VME, с установленными на ней электронными компонентами. Размер печатной платы составляет 234 x 160 мм.

Рисунок 3 – Проект печатной платы модуля

Модуль аналоговых интерфейсов разработан для возможности функционирования при температуре окружающей среды в диапазоне минус 40° – плюс 50° градусов Цельсия, в связи с чем произведен поиск и осуществлен выбор всей элементной базы в соответствии с требуемым

температурным диапазоном функционирования, а также учтены тепловые коэффициенты при проектировании печатных плат.

В рамках решения второй задачи ввиду использования множество кодеков и транскодеров, которые требуют внешней синхронизации, разработана единая система синхронизации ИКМ кодеков, удовлетворяющая требованиям микросхем кодеков Si 3050, Si 3210, TLV320AI22, транскодеров ZL38010, и интерфейсов SPI для микро-ЭВМ STM32H743 [8] которая реализует алгоритм транскодирования SPEEX.

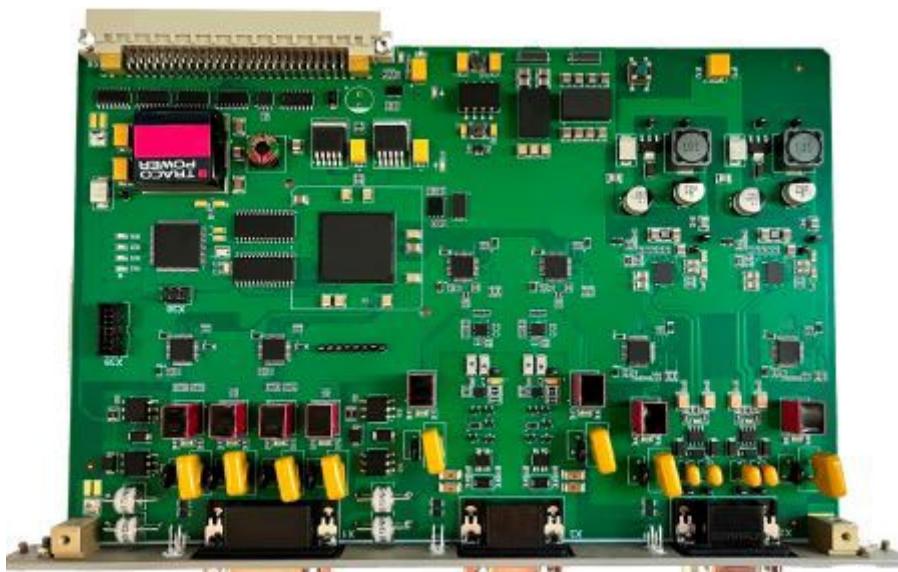

Рисунок 4. Модуль аналоговых интерфейсов.

На рис. 5 приведена схема синхронизации ИКМ указанных микросхем с номенклатурой цепей синхронизации и допустимыми значениями параметров сигналов синхронизации.

Все сигналы системы синхронизации должны быть синхронизованы между собой и с тактовой частотой передачи (приема) группового сигнала мультиплексора. Тактовая частота передачи мультиплексора может быть в диапазоне от 8 кГц до 13 МГц, поэтому для синхронизации тактовых частот подсистемы ИКМ целесообразно использовать метку цикла группового сигнала с периодом 0,5, 5 или 20 мс.

- с помощью схемы синтезатора частоты с ФАПЧ сформирована частота MCLK для ИМС TLV320AI22 со значением 32,768 МГц;

- тактовые частоты BCLK (PCLK) формировались путем деления частоты MCLK на 4 (4096 кГц), частота FSYNC 8 кГц сформирована путем дальнейшего деления частоты MCLK;

- ИМС транскодеров ZL38010 используются в режиме SSI;

- тактовую частоту интерфейсов SPI (2 шт.) для связи с микро-ЭВМ принята равной частотам BCLK (PCLK), т.е. 4096 кГц;

- временные параметры сигналов FSYNC, ENB1, ENB2 заданы в соответствии с параметрами ИМС кодеков.

Рисунок 5. – Схема синхронизации ИКМ

В рамках решения второй задачи разработан узел формирования и распределения цифровых каналов интерфейсов FXS, FXO, E&M. Узел обеспечивает упаковку данных речевых сигналов со скоростями передачи 8,

---

16, 24, 32, 64 кбит/с в цикловую и сверхцикловую структуру группового сигнала мультиплексора, демультиплексирование входного группового сигнала в части интерфейсов FXS, FXO, E&M и внутриканальную выдачу сигналов по интерфейсам ИКМ.

Совместно с речевыми сигналами осуществляется обработка и мультиплексирование/демультиплексирование сигналов линейной сигнализации, сопровождающих речевые каналы.

Техреализация сверхциклической синхронизации для всех речевых каналов, реализована путем передачи метки начала сверхцикла 20 мс в заголовке данных цикла.

Анализ возможных вариантов мультиплексирования кодированных данных речевого канала и линейной сигнализации при различных скоростях кодированного сигнала показал следующее.

При скоростях кодированной речи 16, 24, 32, 64 кбит/с мультиплексирование возможно, как в интервале одного цикла, так и интервале одного суперцикла.

При скорости кодирования речи равной 8 кбит/с мультиплексирование возможно только в интервале суперцикла 20 мс, т.к. блок кодированных данных существует только для суперцикла 20 мс – СЦ 20. Указанному интервалу времени соответствуют не менее 8 – 10 отсчетов линейной сигнализации (в двухразрядном коде). При интервале дискретизации 2,0 мс имеем 10 отсчетов т.е. 20 бит.

Мультиплексирование в интервале цикла гораздо проще, однако имеет худшую эффективность (особенно при длительности цикла 0,5 мс) и не позволяет обеспечить простую реализацию передачи речи, кодированной со скоростью 8 кбит/с.

Использование кодирования речи со скоростями 8 кбит/с и ниже ухудшает качество речи и приводит к существенному усложнению схемы

---

---

мультиплексирования. Необходимость его использования имеется при ограниченной полосе частот радиоканала (32 – 128 кГц) при работе в L-диапазоне частот.

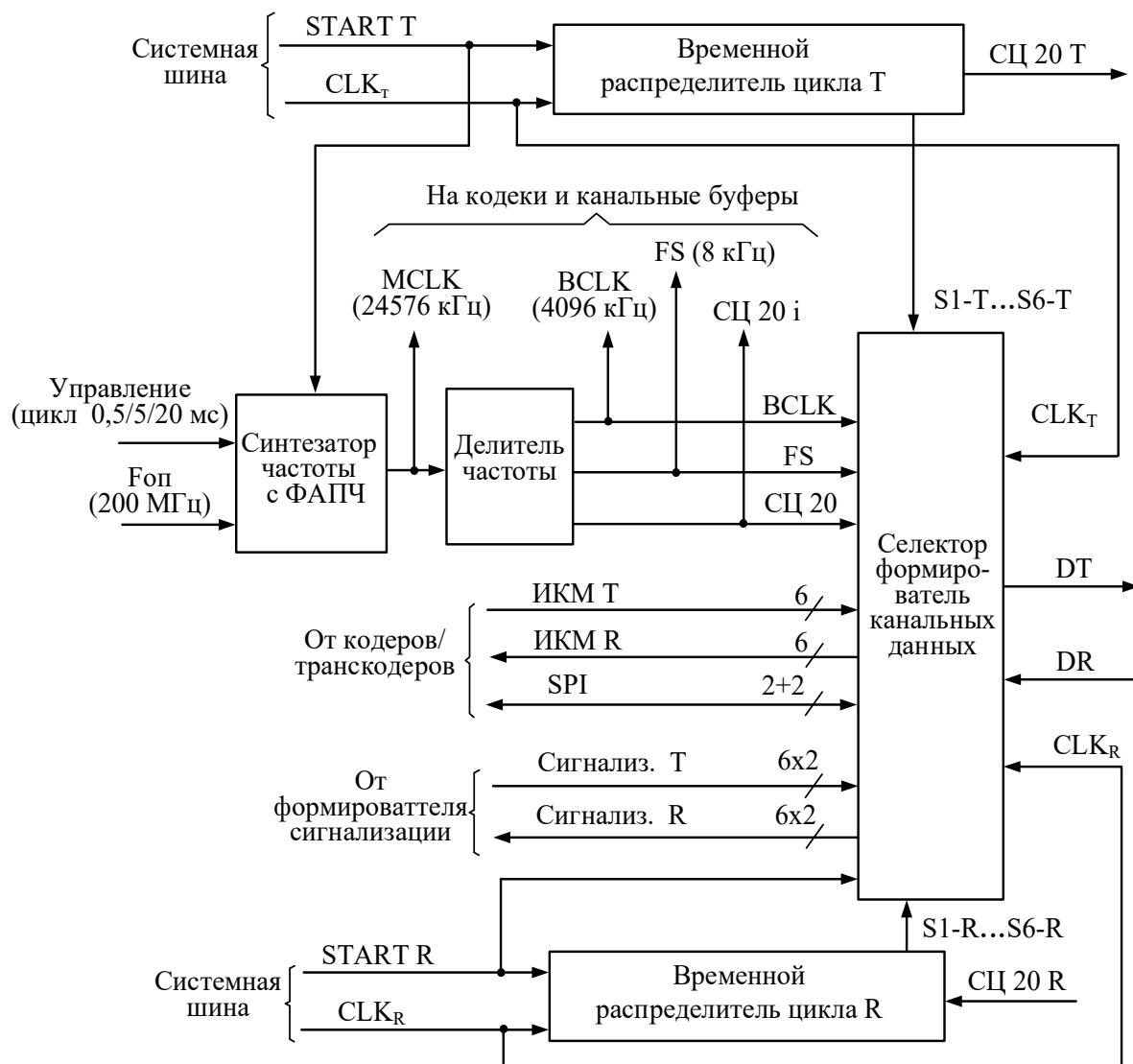

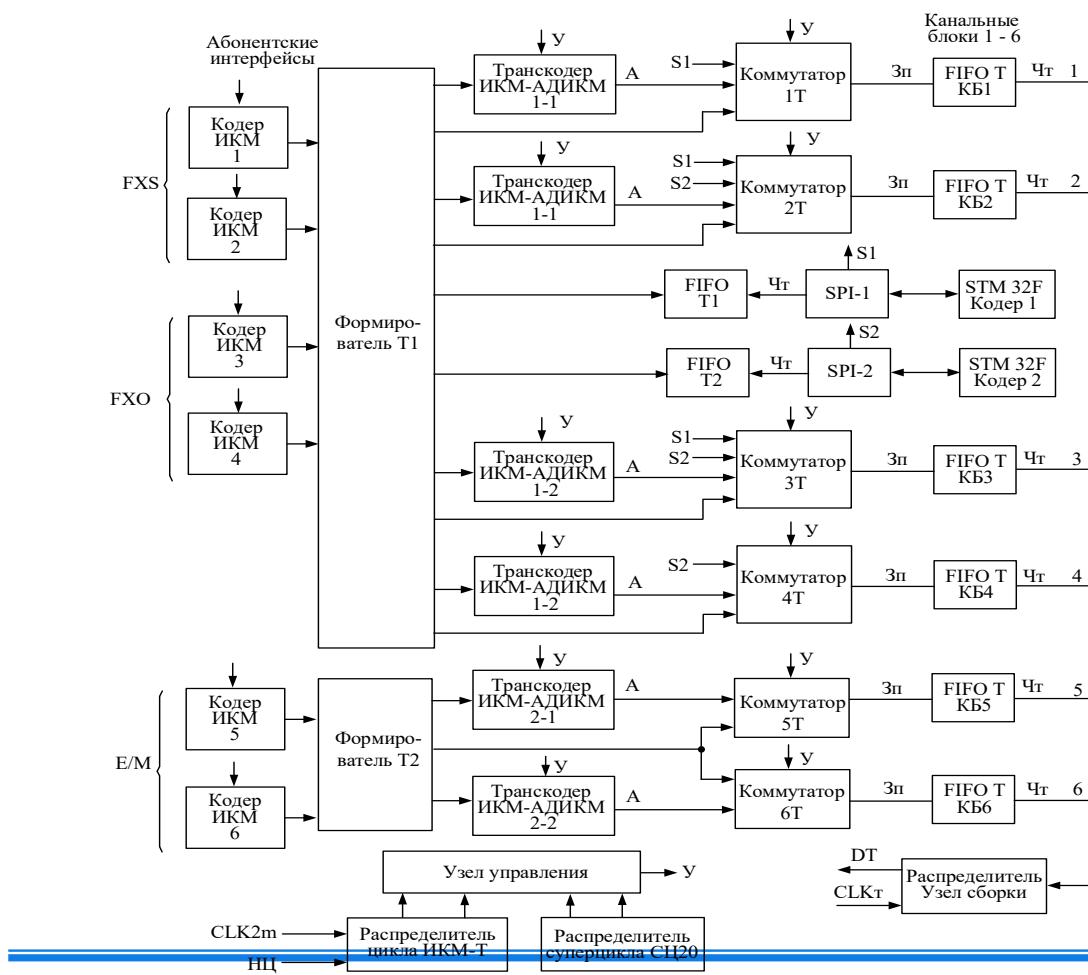

Структурная схема узла приведена на рис. 6 [9]. На вход узла поступают сигналы системной шины следующего назначения:

- START T, CLK<sub>T</sub> – для синхронизации передающей части;

- START R, CLK<sub>R</sub> – для синхронизации приемной части;

- DR – принимаемый групповой сигнал.

Узел обеспечивает формирование группового сигнала DT с тактовой частотой CLK<sub>T</sub> в части интерфейсов FXS, FXO, E&M.

При необходимости узел формирует сигналы сверхциклической сигнализации СЦ 20 Т и СЦ 20 Р.

Взаимодействие с интерфейсами FXS, FXO, E&M осуществляется по шести линиям ИКМ Т и по шести линиям ИКМ Р с кодеками этих интерфейсов, а также по линиям сигнализации Т и Р.

Необходимость использования суперцикла 20 мс (СЦ 20 Т) вызвана спецификой кодирования речи со скоростью 8 кбит/с по алгоритмам G729, SPEEX, где блоку из 160 отсчетов сигнала речи соответствует выходной массив объемом 160 бит с определенной структурой.

Работа узла осуществляется следующим образом:

- синтезатор частоты с помощью ФАПЧ по сигналу START Т формирует тактовую частоту SCLK равную 4,096 МГц для работы кодеков и транскодеров;

Рисунок 6. – Схема узла формирования и распределения цифровых каналов

- сигнал "Управление цикл 0,5/5/20 мс" задает коэффициент деления частоты Fоп в синтезаторе;

- делитель частоты по тактовой частоте SCLK формирует цикл ИКМ с периодом 125 мкс (8 кГц), задаваемый сигналом начала цикла FS, и суперцикл 20 мс СЦ 20 i, включающий 160 циклов ИКМ;

- временные распределители циклов Т и R формируют стробы временных окон сигналов DT и DR, где должны передаваться/приниматься канальные сигналы интерфейсов FXS, FXO, E&M; ширина этих окон в

циклах ГС определяется по таблице 1, а временные позиции в цикле определяются автоматически при создании конкретной конфигурации мультиплексора;

- селектор-формирователь канальных данных обеспечивает все основные функции по транскодированию речи и размещению данных речевых каналов и линейной сигнализации во временных окнах группового сигнала DT для шести каналов, и по извлечению из принимаемого группового потока DR данных речи и линейной сигнализации, обработке и выдаче на кодеки интерфейсов FXS, FXO, E&M в принятом формате взаимодействия (сигналы ИКМ); узел поддерживает три режима кодирования канальных речевых сигналов: ИКМ (64 кбит/с), АДИКМ (32/24/16 кбит/с), SPEEX (8 кбит/с).

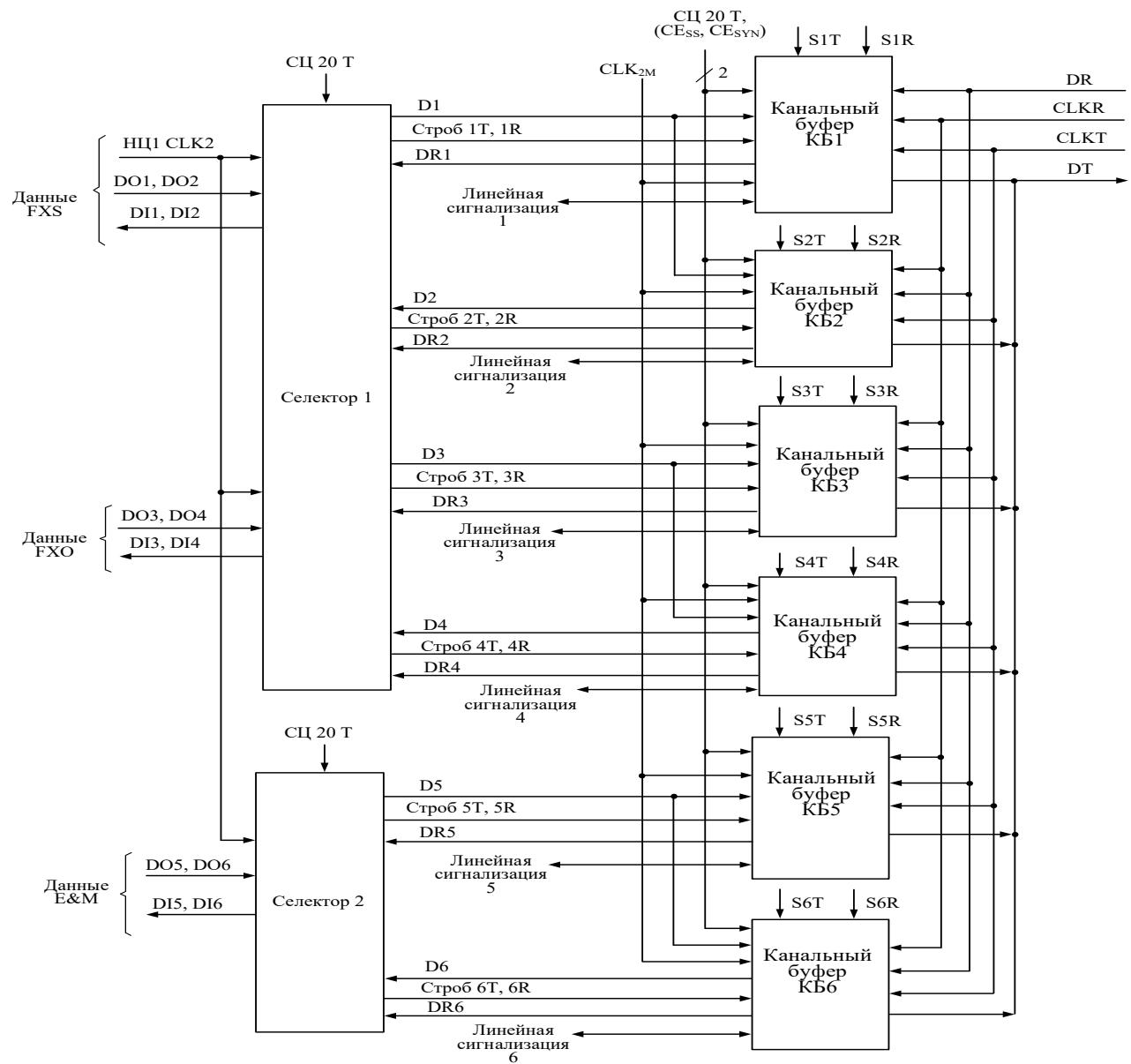

- В рамках решения второй задачи разработана функциональная схема селектора-формирователя канальных данных рис. 7, которая включает два селектора данных и шесть канальных буферов. которая включает два селектора данных и шесть канальных буферов.

Т а б л и ц а 1

| Длительность цикла/сверхцикла, мс | Наименование параметра   | Интерфейс и скорость, кбит/с |     |     |     |      |

|-----------------------------------|--------------------------|------------------------------|-----|-----|-----|------|

|                                   |                          | Речь                         |     |     |     |      |

|                                   |                          | 8                            | 16  | 24  | 32  | 64   |

| 1                                 | 2                        | 3                            | 4   | 5   | 6   | 7    |

| 20/20                             | Количество бит пакета    | 200                          | 360 | 520 | 680 | 1320 |

|                                   | Количество служебных бит | 40                           | 40  | 40  | 40  | 40   |

|                                   | Количество бит данных    | 160                          | 320 | 480 | 640 | 1280 |

| Длительность цикла/сверхцикла, мс | Наименование параметра   | Интерфейс и скорость, кбит/с |    |     |     |     |

|-----------------------------------|--------------------------|------------------------------|----|-----|-----|-----|

|                                   |                          | Речь                         |    |     |     |     |

|                                   |                          | 8                            | 16 | 24  | 32  | 64  |

| 1                                 | 2                        | 3                            | 4  | 5   | 6   | 7   |

| 1                                 | 2                        | 3                            | 4  | 5   | 6   | 7   |

| 5/20                              | Количество бит субпакета | 50                           | 90 | 130 | 170 | 330 |

|                                   | Количество служебных бит | 10                           | 10 | 10  | 10  | 10  |

|                                   | Количество бит данных    | 40                           | 80 | 120 | 160 | 320 |

| 0,5/20                            | Количество бит субпакета | 5                            | 9  | 13  | 17  | 33  |

|                                   | Количество служебных бит | 1                            | 1  | 1   | 1   | 1   |

|                                   | Количество бит данных    | 4                            | 8  | 12  | 16  | 32  |

Селектор 1 обеспечивает работу с четырьмя входными и четырьмя выходными потоками ИКМ интерфейсов FXS, FXO и управляет работой четырех канальных буферов КБ1 – КБ4.

Селектор 2 работает с двумя входными и с двумя выходными потоками ИКМ интерфейса E&M и управляет работой канальных буферов КБ5, КБ6.

КБ1 – КБ6 обеспечивают накопление кодированного сигнала речи в FIFO Т и данных линейной сигнализации в соответствующем обработчике и выдачу накопленных данных канала совместно с линейной сигнализацией на выход группового сигнала DT во временных интервалах, определяемых временными стробами S1T – S6T временного распределителя цикла Т.

КБ1 – КБ6 обеспечивают селекцию из сигнала DR кодированных канальных данных и линейной сигнализации с временных позиций сигнала, определяемых временными стробами S1R – S6R, автономную суперцикловую синхронизацию канальных сигналов, разделение их на данные речи и данные линейной сигнализации и накопление их в приемных буферах в течение суперцикла СЦ 20 R, далее выдачу данных из буферов по запросу селектора.

### Рисунок 7. – Схема селектора-формирователя

Данные линейной сигнализации с разрешением 2,0 мс передаются на ИМС интерфейсов FXS, FXO, E&M.

Селектор 1 обслуживает интерфейсы FXS, FXO и должен обеспечивать образование дуплексных пар FXS ↔ FXO. Образование дуплексных пар FXS ↔ FXO может быть обеспечено по одному из вариантов:

- в конфигурациях двух взаимодействующих мультиплексоров одном из них к одному выделенному окну подключают интерфейс FXS, а во втором – интерфейс FXO; при этом в одном из интерфейсов, например, в FXO цепь передачи линии (КБ) подключить к входу приема интерфейса FXO, а цепь приема линии подключить к цепи передачи интерфейса FXS;

- конфигурации взаимодействующих мультиплексоров принять одинаковыми, но в селекторе данных один из интерфейсов, например, FXO подключить к линии интерфейса FXS.

Селектор 2 обслуживает интерфейсы E&M и может работать автономно. В селекторе 2 нет необходимости обеспечивать работу со скоростью канального сигнала 8 кбит/с и ниже.

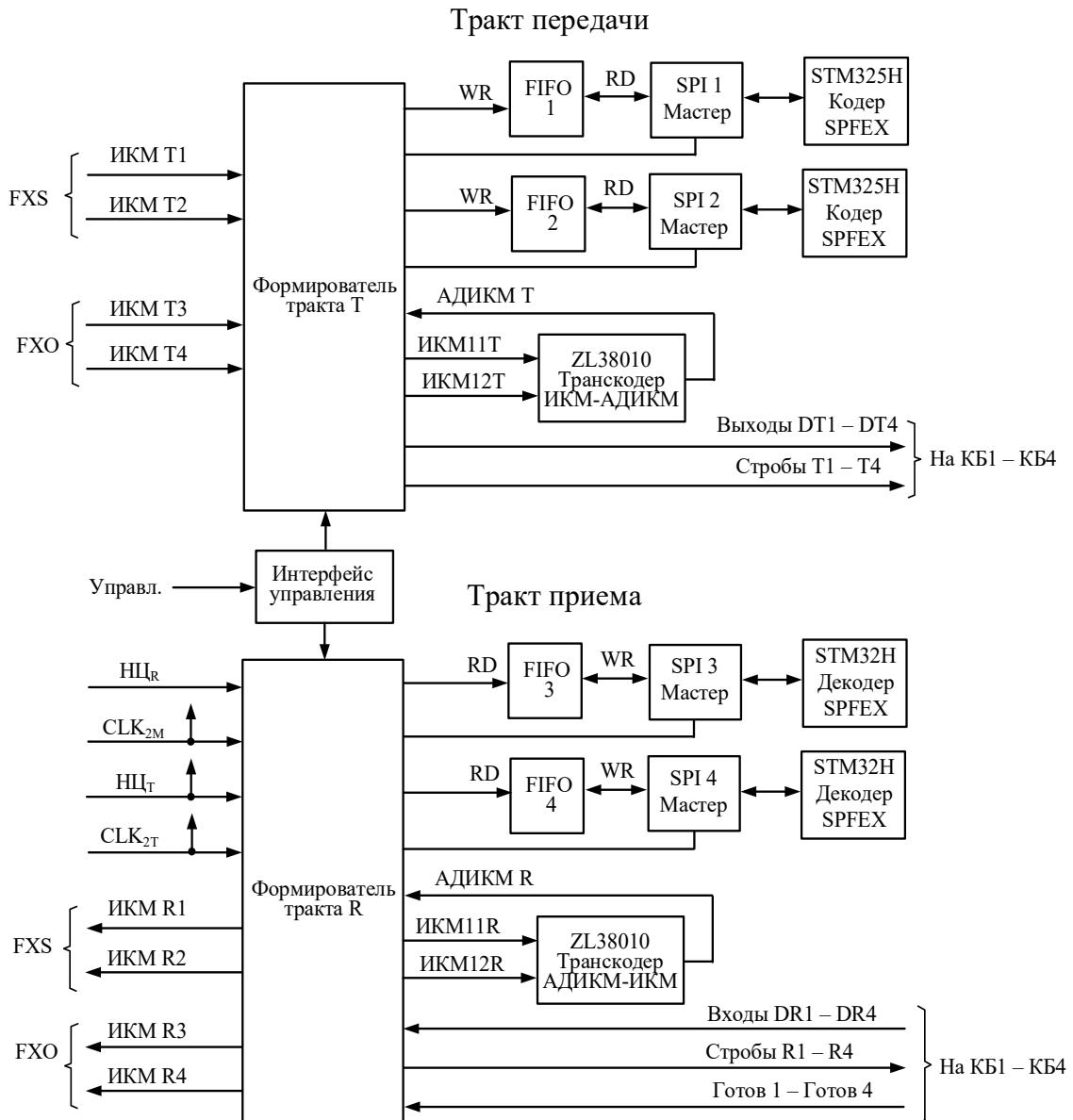

На рис. 8 приведена структурная схема селектора 1 (ГОСТ 27232-87. Стык аппаратуры передачи данных с физическими линиями. Основные параметры. Дата введения 01.01.1988 – М.: Стандартинформ. 1987. 7 с), содержащего тракт приема и тракт передачи. В состав селектора входят:

- 4-х канальный дуплексный транскодер ИКМ↔АДИКМ на микросхеме ZL38010;

- 2-х канальный дуплексный транскодер "Линейная ИКМ – SPEEX" со скоростью кодирования 8 кбит/с; транскодер реализован на базе микро-ЭВМ STM32H743, реализующей функции двух кодеров и двух декодеров;

взаимодействие транскодера с внешними узлами с помощью четырех интерфейсов SPI мастер;

- функциональные узлы "Формирователь тракта Т", "Формирователь тракта R", FIFO 1 – FIFO 4, интерфейс управления, 4 интерфейса SPI, реализованные на ПЛИС XC7A75T.

Рисунок 8. – Структурная схема селектора 1

Селектор 1 обеспечивает кодирование и декодирование данных канальных интерфейсов FXS, FXO в следующих режимах:

- ИКМ;

- АДИКМ со скоростями кодирования 32, 24, 16 кбит/с;

- SPEEX со скоростью кодирования 8 кбит/с (только два канала).

В режиме ИКМ работа узла осуществляется следующим образом.

В передающем тракте сигналы интерфейсов FXS, FXO (ИКМ Т1 – ИКМ Т4) через формирователь тракта Т выдаются на выходы DT1 – DT4 побайтно в последовательном коде с периодом цикла 125 мкс на системной тактовой частоте CLK<sub>2M</sub> для записи в FIFO Т, КБ1 – КБ4. Формирователь тракта Т осуществляет формирование временных окон Строб Т1 – Строб Т4 длительностью 8 тактов, разрешающих запись в КБ1 – КБ4.

В приемном тракте формирователем тракта R циклически, с периодом 125 мкс, формируются временные окна длительностью 8 тактов (Стробы R1 – R4) разрешающие считывание байта данных с FIFO R канальных блоков КБ1 – КБ4; считанные данные поступают через входы DR1 – DR4 на формирователь тракта R, который осуществляет выдачу этих данных на выходы ИКМ R1 – ИКМ R4 и далее в интерфейсы FXS, FXO в соответствующем окне цикла относительно сигнала НЦ.

В режиме АДИКМ работа узла осуществляется следующим образом.

В передающем тракте сигналы интерфейса FXS объединяются в двухканальный сигнал ИКМ 11Т, а сигналы FXO в двухканальный сигнал ИКМ 12Т. Эти сигналы выдаются на вход транскодера ИКМ – АДИКМ. Транскодированные сигналы АДИКМ с одной из скоростей передачи 32, 24, 16 кбит/с выдаются в 4-х канальный сигнал АДИКМ Т с размещением данных в первых двух байтах сигнала в соответствии со спецификацией микросхемы ZL38010. Указанный сигнал через формирователь тракта Т выдается на FIFO Т КБ1 – КБ4. Для селекции данных конкретных каналов и записи их в FIFO Т КБ в формирователе тракта Т формируются 4 временных окна Строб 1 – Строб 4 длительностью 4, 3, 2 бита, в зависимости от скорости кодирования (32, 24, 16 кбит/с).

В приемном тракте в каждом из ИКМ-циклов формируются 4 временных окна Строб 1 – Строб 4 длительностью 4, 3, 2 бита для считывания данных с FIFO R. Считанные данные (выборки 4, 3, 2 бит) FIFO R, КБ, DR1 – DR4 поступают на формирователь тракта R, где объединяются в четырехканальный сигнал АДИКМ R, поступающий на вход транскодера АДИКМ – ИКМ.

Транскодированные сигналы ИКМ с транскодера выдаются в виде двухканальных сигналов ИКМ 11R и ИКМ 12R, которые в формирователе тракта R разделяются на одноканальные сигналы ИКМ R1 – ИКМ R4, выдаваемые на кодеки интерфейсов FXS, FXO. Основой для формирования сигналов Строб T1 – Строб T4, Строб R1 – Строб R4, сигналов ИКМ 11T, ИКМ 12T, и разделения сигналов ИКМ 11R и ИКМ 12R, разделения сигналов АДИКМ является сигнал начала цикла НЦт, поступающий с формирователя СЦ 20 Т.

В режиме SPEEX кодирование и декодирование осуществляется только для двух каналов интерфейсов FXS, FXO в сочетаниях 2FXS, 2FXO, FXS+FXO. Остальные каналы не используются или используют декодирование ИКМ/АДИКМ. Работа в режиме SPEEX осуществляется в следующем порядке.

Кодеки интерфейсов FXS, FXO в этом режиме работают с 16 разрядным линейным кодированием (сигналы ИКМ T1 – ИКМ T4, ИКМ R1 – ИКМ R4).

Четыре интерфейса SPI используются для работы кодеками SPEEX, G729 и др., реализованными на микросхеме STM32H, при кодировании речи со скоростями 8 кбит/с и ниже. При этом два интерфейса SPI связаны с кодерами речевого сигнала, а два с декодерами. Обмен данными по этим интерфейсам осуществляется пакетами данных, соответствующим временному интервалу суперцикла 20 мс (СЦ 20).

Размеры пакетов:

- $160 \times 16$  бит – исходный сигнал речи в линейном 16 разрядном коде;

- 160 бит – кодированный сигнал речи для передачи в линии связи.

В передающем тракте формирователь тракта Т выбирает два канала из 4-х входных (ИКМ Т1 – ИКМ Т4) и циклически, с интервалом 125 мкс, осуществляет запись данных этих каналов в FIFO 1 и FIFO 2. Формирователь тракта Т за 10/5 мс до окончания СЦ 20Т выдает разрешение на SPI-1 и SPI-2 (с разносом по времени) для кодирования данных с FIFO 1 (2). SPI мастера, при незанятой микро-ЭВМ STM32H, считывают с FIFO 1 (2) блок данных ( $160 \times 16$ ) бит и передают его в микро-ЭВМ. После кодирования блока данных SPI мастер считывает кодированные данные с микро-ЭВМ (блок данных 160 бит) и через формирователь тракта Т записывает их в FIFO Т одного из КБ. Длительность сигналов Строб Т при этом должна быть 160 бит.

В приемном тракте по сигналу Готов 1 (2 – 4) формирователь тракта R выдает на SPI-3 и SPI-4 запросы на декодирование данных. При незанятой микро-ЭВМ, интерфейс SPI-3 (4) считывает через формирователь тракта R блок данных 160 бит с FIFO R соответствующего КБ и передает его в микро-ЭВМ для декодирования. После декодирования блока SPI мастер переписывает блок декодированных данных ( $160 \times 16$  бит) из микро-ЭВМ в FIFO 3 (4).

Формирователь тракта R циклически в каждом цикле ИКМ считывает данные из ОЗУ 3 (4) и распределяет их на два выбранных интерфейса ИКМ R<sub>i</sub> на требуемой позиции цикла ИКМ.

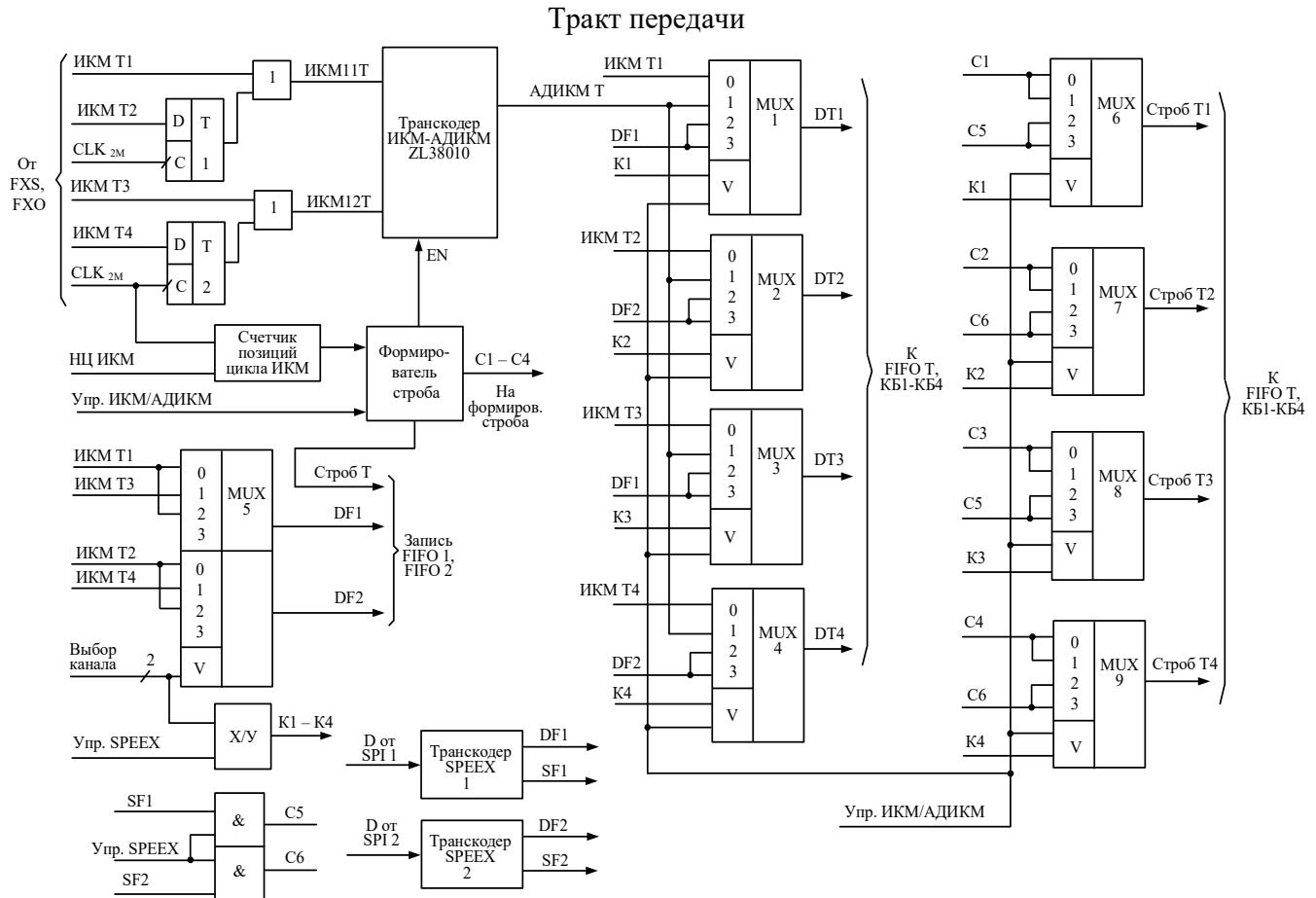

На рис. 9 приведена функциональная схема тракта передачи селектора.

Назначение основных функциональных элементов тракта передачи следующее: мультиплексоры MUX1 – MUX4 осуществляют выбор сигналов данных для записи в FIFO Т КБ1 – КБ4 в трех режимах: ИКМ, АДИКМ, SPEEX;

- мультиплексоры MUX6 – MUX9 осуществляют выбор сигналов разрешения записи данных в FIFO Т КБ1 – КБ4;

Рисунок 9. – Схема тракта передачи селектора 1

- счетчик позиций цикла ИКМ и формирователь стробов обеспечивают формирование сигналов разрешения записи данных в FIFO Т КБ и FIFO транскодера SPEEX в различных режимах;

- мультиплексор MUX5 обеспечивает выбор двух сигналов интерфейсов FXS и FXO из 4-х доступных по одному из трех вариантов, указанных в таблице 2;

- преобразователь X/Y преобразует код выбора каналов в 4 сигнала K1 – K4, управляющих выбором сигналов данных и сигналов стробов записи в мультиплексорах MUX1 – MUX4 и MUX6 – MUX9, в режиме SPEEX.

Т а б л и ц а 2

| Схема выбора | Код выбора | Значения сигналов |    |    |    |

|--------------|------------|-------------------|----|----|----|

|              |            | K1                | K2 | K3 | K4 |

| 2 FXS        | 00         | 1                 | 1  | 0  | 0  |

| 2 FXO        | 01         | 0                 | 0  | 1  | 1  |

| FXS + FXO    | 10         | 1                 | 0  | 0  | 1  |

Два канала транскодера SPEEX включают ОЗУ, интерфейс SPI мастер и микро-ЭВМ.

В режиме ИКМ данные интерфейсов FXS, FXO в формате 8 битовой ИКМ поступают через мультиплексоры MUX1 – MUX4 на FIFO Т КБ1 – КБ6. Сигналы временных стробов Строб 1 – Строб 4 совпадают во времени и селектируют данные ИКМ 8 бит.

В режиме АДИКМ данные входных потоков ИКМ 1 – ИКМ 4 преобразуются в двухканальные сигналы ИКМ 11T и ИКМ 12T, необходимые для работы транскодера ZL38010. На выходе транскодера сигнал АДИКМ формируется как 4-х канальный сигнал в 4-х битовых слотах первых двух 8-ми битовых слотов. Этот сигнал через мультиплексоры MUX1 – MUX4 выдаются на FIFO Т КБ1 – КБ4. В этом режиме формирователь стробов обеспечивает выдачу сигналов Строб 1 – Строб 4 сдвинутых на 4 бита относительно предыдущего. Ширина строба 4/3/2 бита в зависимости от скорости кодирования (32/24/16 кбит/с). При этом в каждом КБ в данном

---

цикле ИКМ обеспечивается запись 4/3/2 бит сигнала данных АДИКМ в FIFO Т.

В режиме SPEEX кодеки интерфейсов FXS, FXO должны работать с 16 разрядной линейкой ИКМ. Мультиплексор MUX1 выбирает из 4-х входных сигналов два для кодирования SPEEX в соответствии с заданием (таблица 1). 16-ти разрядные выборки этих сигналов по сигналу C7R записываются в FIFO двух транскодеров SPEEX.

С временного распределителя суперцикла СЦ 20 на SPI-мастер транскодера SPEEX выдаются сигналы, разрешающие считывание данных с ОЗУ за 10 мс и 5 мс до конца СЦ 20. При незанятой микро-ЭВМ SPI-мастер обеспечивает считывание данных с ОЗУ и трансляцию на микро-ЭВМ (блок данных 160 отсчетов –  $160 \times 16$  бит); после кодирования сигнала с микро-ЭВМ считывается блок данных 160 бит, который записывается в FIFO соответствующего КБ следующим образом.

При считывании данных SPI-мастер формирует временной строб SF1 (SF2), длиной 160 бит, который поступает на мультиплексоры стробов MUX6 – MUX9. С транскодера данные DF1, DF2 выдаются на входы соответствующих мультиплексоров данных MUX1 – MUX4 с помощью сигналов K1 – K4 преобразователя кодов X/Y в мультиплексоре одного из каналов (MUX6 – MUX9). Строб данных SF1/SF2 (C5, C6) выдается на FIFO Т КБ и обеспечивает запись данных с выхода транскодера (DF1, DF2).

Таким образом, в FIFO Т двух канальных блоков к концу текущего суперцикла СЦ 20 оказываются записанными блоки кодированных данных объемом 160 бит.

В последнем ИКМ цикле СЦ 20 в FIFO Т КБ записываются дополнительные 40 бит (сигнализация+SYNC) и итоговая длина блока данных СЦ 20 в канале составляет  $160+40=200$  бит. На рис. 10 приведена функциональная схема тракта приема селектора 1.

---

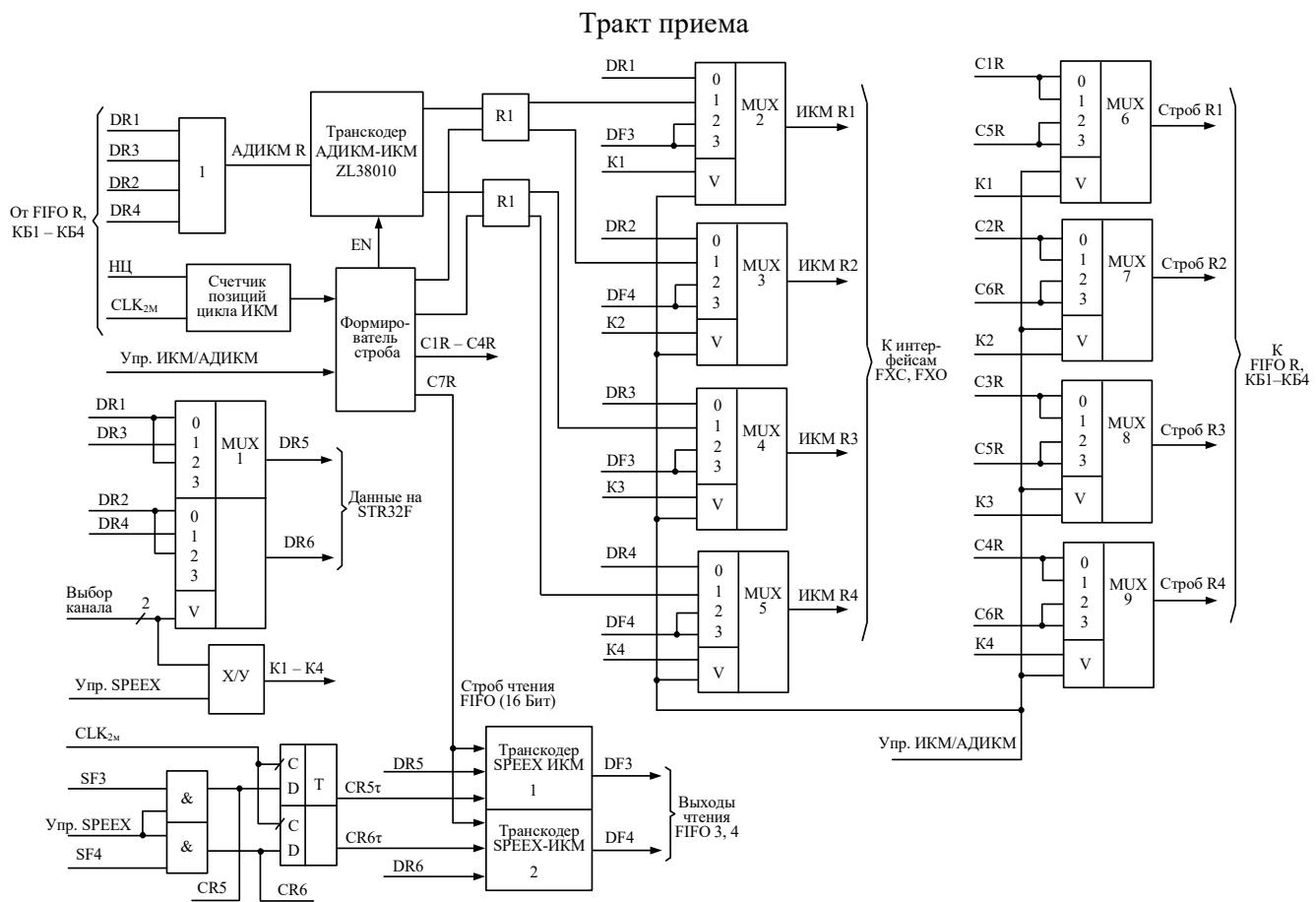

Назначение основных функциональных элементов тракта следующее:

- мультиплексоры MUX2 – MUX5 осуществляют выбор источника данных, формирующего данные приема для интерфейсов FXS и FXO для трех режимов ИКМ, АДИКМ, SPEEX;

Рисунок 10. – Схема тракта приема селектора 1

- мультиплексоры MUX6 – MUX9 осуществляют выбор сигнала, разрешающего считывание данных с FIFO R КБ1 – КБ4 для указанных выше режимов;

- счетчик позиций цикла ИКМ и формирователь стробов обеспечивают формирование сигналов, разрешающих считывание данных с FIFO R КБ1 – КБ4 и с ОЗУ 3 трактов SPEEX в различных режимах;

- мультиплексор MUX4 обеспечивает выбор двух сигналов двух КБ из 4-х входных, используемых в режиме SPEEX, для транскодирования SPEEX-линейная ИКМ в двух транскодерах;

- преобразователь X/Y преобразует код выбора каналов для режима FXS, FXO в 4 сигнала K1 – K4, управляющих выбором сигналов данных и временных стробов считывания данных с FIFO R КБ в мультиплексорах MUX2 – MUX9.

В режиме ИКМ формирователь стробов циклически с интервалом времени цикла ИКМ (125 мкс) формирует сигналы стробов C1R – C4R совпадающие по времени, обеспечивающие через мультиплексоры MUX6 – MUX9 разрешение считывания отсчетов 8 бит с FIFO R КБ1 – КБ4. Считанные данные с этих FIFO R через мультиплексоры MUX2 – MUX5 выдаются на интерфейсы FXS, FXO.

В режиме АДИКМ формирователь стробов обеспечивает формирование четырех временных стробов C1R – C4R, сдвинутых друг относительно друга на 4 бита CLK<sub>2M</sub> с шириной строба 4/3/2 такта, в зависимости от скорости кодирования принимаемого сигнала. Считанные с FIFO R данные DR1 – DR4 объединяются при помощи схемы ИЛИ (1) в 4-х канальный сигнал АДИКМ R, поступающий на вход транскодера АДИКМ – ИКМ. Двухканальные сигналы ИКМ с выхода транскодера при помощи схем разделения R1, R2 разделяются на два канала и полученные 4 одноканальные сигналы ИКМ (на определенной позиции цикла ИКМ) через мультиплексоры MUX2 – MUX5 выдаются на интерфейсы FXS, FXO.

В режиме SPEEX работа тракта осуществляется следующим образом:

- мультиплексор MUX1 по команде системы управления выбирает 2 принимаемых канальных сигнала из 4-х входных (DR1 – DR4) и выдает их (DR5, DR6) на два канала транскодера "SPEEX – линейная ИКМ" (интерфейс SPI мастер, микро-ЭВМ STM32H, FIFO);

- преобразователь кодов X/Y по коду выбора каналов формирует сигналы K1 – K4, управляющие выбором сигналов в мультиплексорах MUX2 – MUX9;

- после поступления в КБ выбранных каналов данных полного СЦ 20R, по сигналу "Готовность D" КБ интерфейс SPI мастер при незанятой микро-ЭВМ STM32H формирует сигналы считывания данных SF3 (CR5) и SF4 (CR6) с шириной окна 200 бит, которые через мультиплексоры MUX6 – MUX9 выдаются на FIFO R двух выбранных КБ;

- считанные данные с FIFO R двух КБ поочередно через мультиплексор MUX1 поступают на транскодер "SPEEX – линейная ИКМ" (DR5, DR6);

- после транскодирования данных СЦ 20R 160 отсчетов с линейной 16-ти разрядной ИКМ записываются во внутреннее ОЗУ транскодера (ОЗУ 3, ОЗУ 4);

- выборки линейного 16 разрядного кода ИКМчитываются с ОЗУ транскодера (ОЗУ 3, ОЗУ 4) по сигналу строба C7R (сигналы DF3, DF4) и далее через MUX2 – MUX5 распределяются в два выбранных интерфейса FXS, FXO с периодом цикла ИКМ (125 мкс);

- два незадействованных канала при этом могут использоваться в режиме ИКМ или АДИКМ.

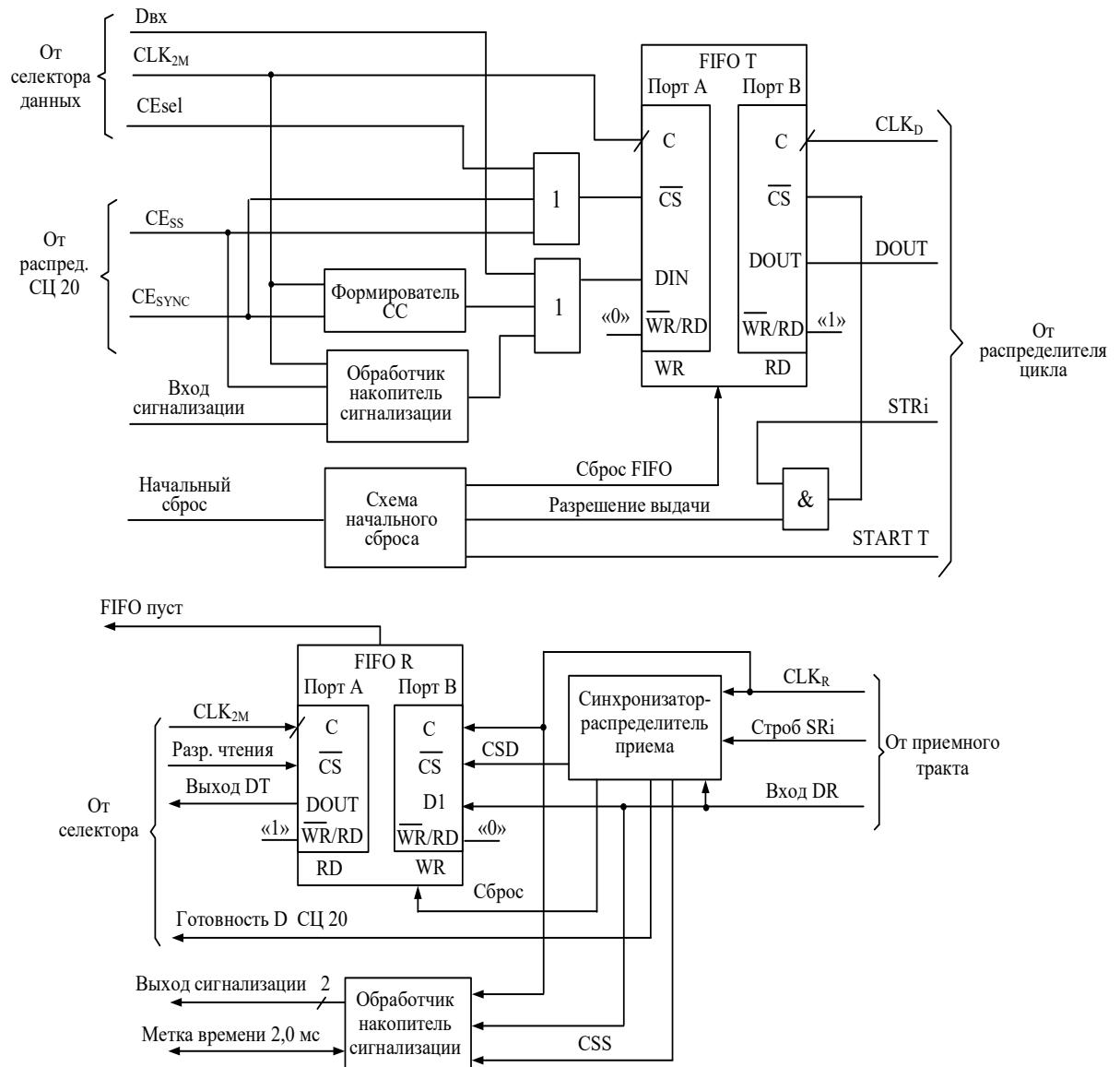

Функциональная схема канального буфера (ГОСТ 25007-81. Стык аппаратуры передачи данных с каналами связи систем передачи с частотным разделением каналов. Основные параметры сопряжения. Дата введения 01.01.1983. – М.: Стандартинформ. 2005. 11 с), ориентированного на внутриканальную суперциковую синхронизацию, приведена на рис. 11.

Канальный буфер (КБ) обеспечивает:

- запись в FIFO T данных канального сигнала с ИКМ-потока или данных с SPI интерфейса;

- прием и обработку линейной сигнализации, накопление данных в интервале суперцикла 20 мс (СЦ 20);

- объединение данных синхросигнала, линейной сигнализации и запись

их в FIFO T после записи данных (в 160-ом ИКМ цикле СЦ 20);

Рисунок 11. – Схема канального буфера

- селекцию из входного сигнала DR данных пакета суперцикла СЦ 20 по временному стробу канала SRi, формируемому времененным распределителем цикла R.

- обнаружение в данных канала суперциклового синхросигнала, обеспечение синхронизации по СЦ 20, и разделение данных на сигнализацию и данные речи;

- запись данных речи в FIFO R;

- обработку данных сигнализации и формирование выходного сигнала линейной сигнализации;

- считывание с FIFO R данных речи по сигналам селектора и выдача их в заданные тайм-слоты ИКМ потока или в интерфейс SPI для последующего декодирования в микро-ЭВМ STM32H743.

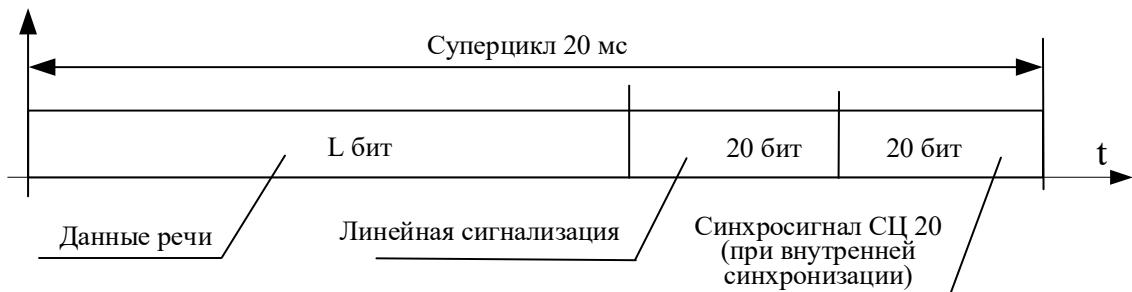

Канальный буфер обеспечивает работу с пакетом данных суперцикла (СЦ 20) структура которого приведена на рис. 12.

Рисунок 12. – Структура пакета данных суперцикла

Формирование пакета данных СЦ 20 в порту А FIFO Т осуществляется следующим образом. Данные кодированной речи записываются в FIFO Т через порт А циклически с периодом 125 мкс для ИКМ и АДИКМ, и с периодом 20 мс при кодировании речи скоростью 8 кбит/с и ниже.

Формирование пакета данных суперцикла 20 мс осуществляется с помощью внешнего распределителя Т СЦ 20. Распределитель Т СЦ 20 работает на тактовой частоте CLK<sub>2M</sub>, и суперцикл включает 160 ИКМ циклов с периодом 125 мкс.

Распределитель формирует два временных окна CE<sub>SYNC</sub>, CE<sub>SS</sub> для выдачи данных синхросигнала (СС), служебной сигнализации, в 160-ом ИКМ цикле СЦ 20. Данные речевого сигнала считаются с порта В FIFO Т. Выдача данных (Вых D) ведется только во временных окнах сигнала Строб STi.

После включения электропитания и в нештатных ситуациях по сигналу "Нач. фазирования" осуществляется сброс FIFO Т и блокировка считывания данных с порта В, на один СЦ 20.

Таким образом, данные, записанные в FIFO Т в текущем СЦ 20 считаются и выдаются на выход в следующем СЦ 20.

Рассмотрим временные соотношения процессов работы при скоростях кодирования 8 кбит/с и ниже процессы кодирования и декодирования данных речи осуществляется для пакета данных в 160 (или др.) отсчетов в целом и время кодирования составляет 3 – 4 мс, а декодирования 0,5 – 1,0 мс. Кроме того, кодеры и декодеры всех каналов работают на одной микро-ЭВМ STM поочередно, что приводит к плавающим задержкам доступа к кодерам и декодерам FIFO. В связи с этим время задержки передачи больше одного суперцикла и, в крайнем случае, может достигать двух суперциклов.

В связи с указанными особенностями требуется разработка алгоритма диспетчеризации работы кодеров и декодеров микро-ЭВМ STM32H743, которая осуществляется через интерфейсы SPI 1 – SPI 4.

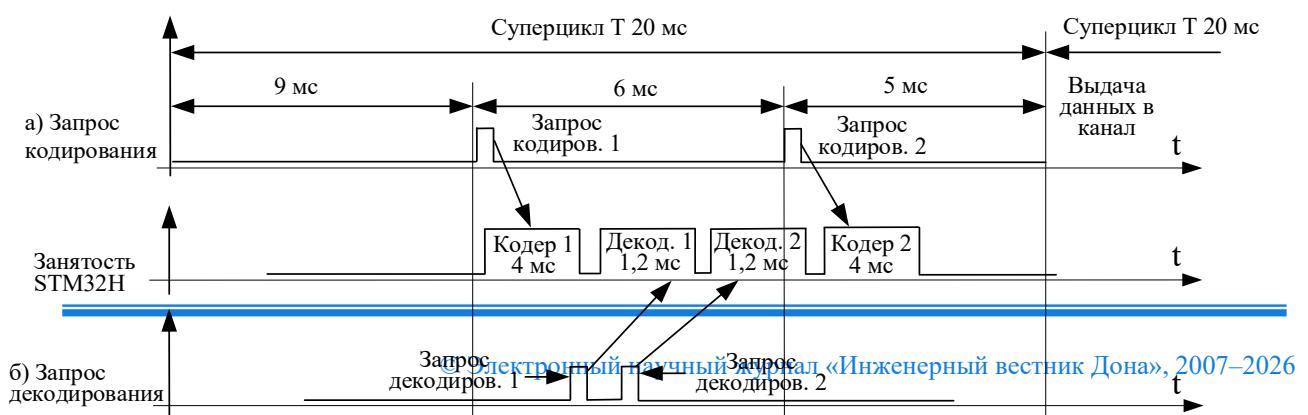

Временное распределение и диспетчеризация запросов на кодирование и декодирование пакетов данных представлена на рис. 13.

### Рисунок 13. – Диспетчеризация запросов

Особенность процесса в том, что начало суперциклов передачи и приема данных могут находиться в случайных соотношениях, т.е. запросы, могут быть сдвинуты относительно запросов передачи на произвольное расстояние.

Исходя из рис. 13 накопление данных передачи целесообразно начинать за 8 – 10 мс до начала суперцикла, и тогда в конце следующего суперцикла будут сформированы кодированные сигналы (блоки длиной 160 бит) для обеих каналов.

Рассмотрев детали мультиплексирования сигналов речевой связи в групповой сигнал мультиплексора и их демультиплексирования применительно к различным вариантам построения и различным периодом цикла группового сигнала. Обоснована необходимость использования сверхциклической синхронизации при скорости кодирования речевого сигнала 8 кбит/с и ниже, показана целесообразность использования внутриканальной сверхциклической синхронизации. Рассмотрены технические решения по реализации функциональных узлов.

Однако рассмотренного недостаточно для практической реализации узла в целом. Необходимо определить детально все функциональные связи между элементами схем мультиплексирования и демультиплексирования:

- канальными кодерами/декодерами ИКМ интерфейсов FXS, FXO, E&M;

- FIFO T и FIFO R канальных блоков (КБ), обеспечивающих связь с выходным сигналом DT и выходным сигналом DR;

- транскодерами ИКМ-АДИКМ и АДИКМ-ИКМ (микросхемы ZL 380100);

- транскодерами со скоростью 8 кбит/с и ниже, реализованными на базе микросхемы STM32H743 и интерфейсах SPI, и FIFO, ориентированных на ПЛИС.

При разработке функциональных схем взаимодействия необходимо учитывать следующие исходные данные и ограничения:

- в каждом из интерфейсов FXS, FXO, E&M реализуют по два независимых канала, итого 6 каналов речи, из которых одновременно могут использоваться от 1-го до 6-ти каналов;

- для интерфейсов E&M используется кодирование ИКМ (64 кбит/с) или АДИКМ (32; 24; 16) кбит/с;

- для интерфейсов FXS, FXO используется кодирование ИКМ, АДИКМ со скоростью 32, 24, 16 кбит/с или специальные коды со скоростью 8 кбит/с и ниже; при этом одновременно кодирование со скоростью 8 кбит/с и ниже обеспечивается только для двух дуплексных пар каналов из общего количества каналов - 4;

- одновременно с данными речевого трафика в пакет (сверхцикл) данных должны включаться данные линейной сигнализации и синхрокомбинации.

На рис. 14 представлена функциональная схема передающего тракта, который содержит следующие элементы:

- 6 кодеров ИКМ, реализованных в СБИС соответствующих абонентских интерфейсов;

- 6 транскодеров ИКМ-АДИКМ, реализованных с помощью двух микросхем

ZL 380100;

- два FIFO Т канальных блоков, реализованных в ПЛИС;

- два кодера речи со скоростью 8 кбит/с, каждый из которых содержит FIFO T, интерфейс SPI (1 2), программный кодер на базе микро-ЭВМ STM32H743;

- функциональные элементы – коммутаторы Т (1...6), обеспечивающие выбор сигнала для канальных блоков и реализованные в ПЛИС;

- групповые элементы распределитель цикла ИКМ-Т, распределитель суперцикла СЦ 20, распределитель – узел сборки, реализованные в ПЛИС, и обеспечивающие организацию связей для всех шести каналов речевой связи.

- На схеме входы транскодеров ИКМ-АДИКМ показаны индивидуально, однако учитывая конкретику микросхемы ZL 800100, следует понимать, что физический вход ИКМ у нее один для двух каналов, а каналы задаются временными стробами ENB1, ENB2.

### Рисунок 14 – Схема передающего тракта

*Примечание - Тактовая частота узлов SPI-1 и SPI-2 должна быть та же, что и в кодерах ИКМ, транскодерах ИКМ-АДИКМ для обеспечения простоты работы с КБ1 – КБ4.*

В схеме выходы 4-х кодеров ИКМ интерфейсов FXS, FXO распределяются на обработку с помощью формирователя T1.

В транскодерах ИКМ – АДИКМ выбирается входной сигнал требуемого кодера абонентского интерфейса путем задания соответствующего временного строба слота.

Схемы прохождения сигналов при различных видах кодирования следующие:

- в режиме "ИКМ" сигнал с соответствующего входа интерфейса через коммутатор соответствующего КБ записывается в FIFO Т этого КБ; запись идет с периодом цикла ИКМ – 125 мкс;

- в режиме "АДИКМ" (скорости 32, 24, 16 кбит/с) 4- х канальный сигнал с выхода транскодера ИКМ – АДИКМ через коммутатор соответствующего КБ поступает в FIFO Т КБ 1 – КБ 4 с периодичностью 125 мкс; запись сигнала в FIFO КБ 1 – КБ 4 осуществляется с помощью 4-х индивидуальных временных стробов, сдвинутых на 4 бита относительно друг друга;

- в режиме SPEEX в одном или двух кодерах ИКМ устанавливается режим выдачи линейного кода, выборки которого накапливаются в FIFO Т1 (T2) в течение суперцикла 20 мс (160 отсчетов), после чего по сигналу распределителя суперцикла СЦ 20 через интерфейс SPI-1 выдаются на кодер 1 (2) STM32H; после кодирования данных в STM32H интерфейс SPI-1 (2) считывает блок кода длиной 160 бит и через коммутатор назначенного КБ

(сигнал S1, S2) считываемые данные записывает в FIFO Т назначенного блока.

КБ объединяет кодовый блок с данными линейной сигнализации и синхрокомбинации суперцикла и выдает в групповой выходной сигнал во временных окнах, задаваемых распределителем - узлом сборки.

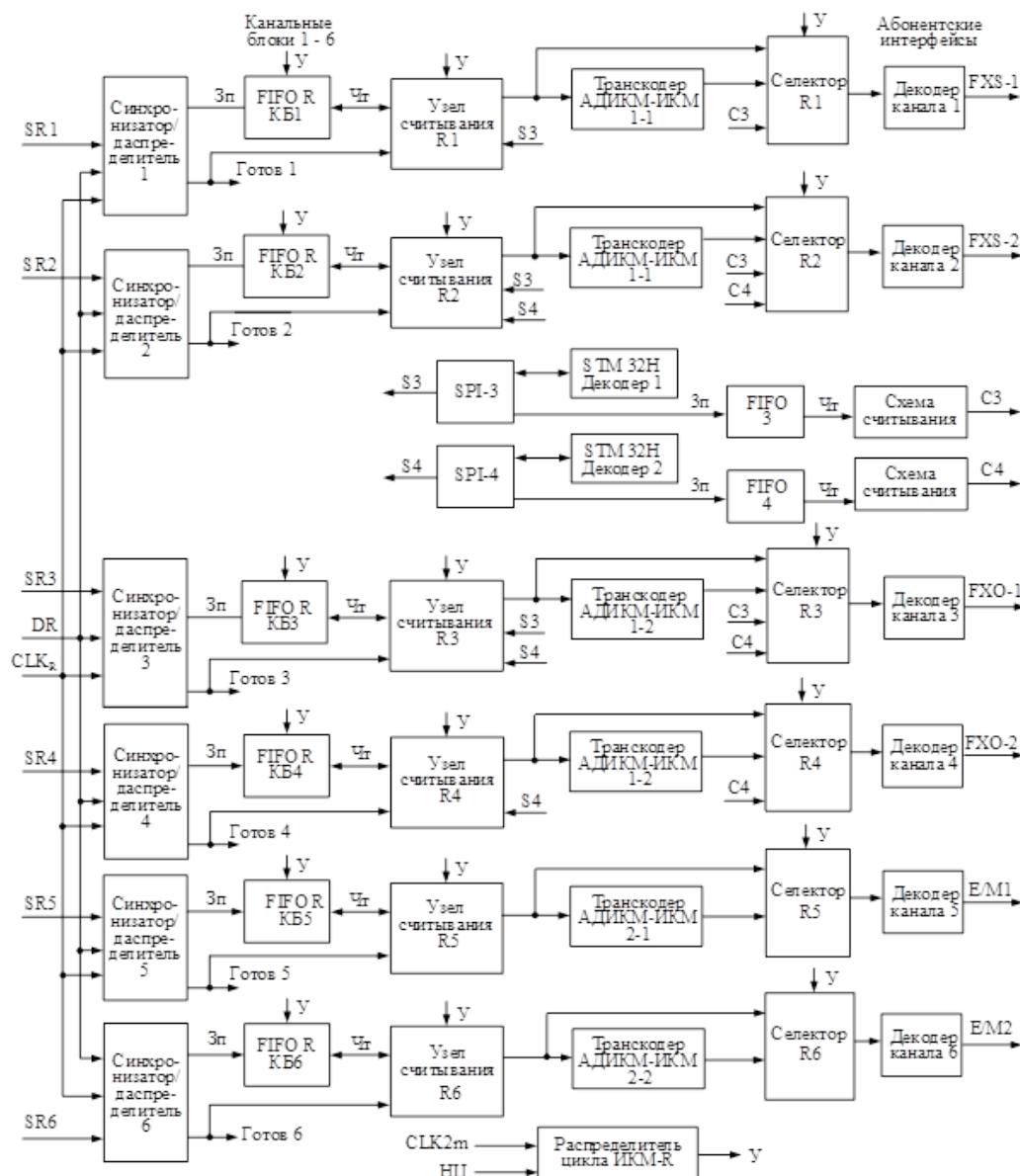

На рис. 15 представлена функциональная схема тракта приема, который содержит следующие элементы:

- шесть канальных синхронизаторов-распределителей данных, обеспечивающих селекцию из группового сигнала DR данных до шести речевых каналов, суперцикловую внутриканальную синхронизацию, демультиплексирование канальных пакетов суперцикла на данные линейной сигнализации и данные речевого сигнала, выдачу сигналов "Готов 1" – "Готов 6" после приема данных суперцикла конкретного канала;

- шесть FIFO R из состава канальных блоков КБ1 – КБ6, в которые записываются данные канальных речевых сигналов;

- шесть узлов считывания R1...R6, обеспечивающих считывание данных с FIFO R КБ после поступления сигнала "Готов" и распределяющих считанные данные на один из обработчиков канального сигнала:

1. транскодер АДИКМ-ИКМ;

2. селектор соответствующего абонентского интерфейса;

3. два транскодера сигналов со скоростью кодирования 8 кбит/с;

- шесть транскодеров АДИКМ-ИКМ, реализованных с помощью двух микросхем ZL380100;

- два тракта транскодеров кодов со скоростью 8 кбит/с и ниже в линейный 16-разрядный код ИКМ, каждый из которых содержит интерфейс SPI (3, 4), программный декодер на базе STM32H743 и FIFO (3, 4) со схемой считывания; в FIFO (3,4) записываются 160 отсчетов декодированного речевого сигнала в линейном шестнадцатиразрядном коде ИКМ;

- шесть селекторов R1...R6, обеспечивающих выбор сигналов для декодеров абонентских интерфейсов FXS, FXO, E&M:

1. ИКМ отсчеты с узлов считывания R (FIFO R);

2. ИКМ отсчеты с транскодера АДИКМ-ИКМ;

3. ИКМ отсчеты с ОЗУ (3, 4) транскодеров 8 кбит/с;

- групповое оборудование, включающее распределитель цикла ИКМ-R.

Рисунок 15. – Схема приемного тракта

*Примечание - Тактовая частота схем SPI-3 и SPI-4 считывания FIFO 3, FIFO 4 должна быть та же, что в транскодерах АДИКМ-ИКМ для простоты работы с декодерами 1 – 4 и КБ1 – КБ4.*

Формирование входных сигналов для транскодеров АДИКМ-ИКМ должно осуществляться в двух временных слотах сигнала АДИКМ в соответствии с тех описанием микросхемы ZL380100C.

Все описанные выше технические решения и алгоритмы были реализованы на ПЛИС в виде прошивок, без использования готовых IP-ядер, с целью обеспечения возможности дальнейшей сертификации.

По результатам работы по разработке модуля аналоговых интерфейсов, входящего в состав гибкого мультиплексора был получен патент на

изобретение RU 2832563.

Рисунок 16. – Патент RU 2832563

### ***Выходы***

- 1) Благодаря разработанному модулю аналоговых интерфейсов спутниковый мультиплексор получил возможность работать с абонентским оборудованием в 2х или 4х проводном режиме по протоколам FXO (2 канала), FXS (2 канала), E&M (2 канала), на скоростях 8 – 64 кбит/с.

- 2) Обеспечена возможность сертификации модуля аналоговых интерфейсов.

### ***Литература***

- 1.Бугаевский А.Н. Мультиплексор. Патент на полезную модель RU 2690785, МПК H04L 29/04, H04J 3/00. РФ. Заявл. 11.01.2018. Опубл. 05.06.2019. Заявитель и патентообладатель ООО «Микролинк-связь». URL: elibrary.ru/download/elibrary\_39389535\_81975228.PDF.

2. Олифер В.Г., Олифер Н.А. Компьютерные сети. Принципы, технологии, протоколы: Учебник для вузов. 3-е изд. – СПб: Питер, 2008. – 958 с.

3. Микушин А.В., Сажнев А.М., Сединин В.И. Цифровые устройства и микропроцессоры. – СПб: БХВ-Петербург, 2010. – 832 с.

4. Шило В.Л. Популярные цифровые микросхемы. – М.: Радио и связь, 1987. – 352 с.

5. Уэйкерли Дж. Ф. Проектирование цифровых устройств. – М.: Постмаркет, 2002. – 544 с.

6. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. – М.: Мир, 2001. – 379 с.

7. Угрюмов Е.П. Цифровая схемотехника. – СПб: БХВ-Петербург, 2004. – 528 с.

8. Букреев И.И., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. – М.: Техносфера, 2009. – 714 с.

9. Брякин Л.А. Электротехника и электроника: Конспект лекций. – Пенза: Изд-во ПГУ, 2004. – 152 с.

### References

1. Bugaevskij A.N. Mul'tiplexor. [Multiplexer]. Patent na poleznuyu model' RU 2690785, MPK H04L 29/04, H04J 3/00. RF. zayavl. 11.01.2018. opubl. 05.06.2019. Zayavitel' i patentoobladatel' OOO «Mikrolink-svyaz». URL: elibrary.ru/download/elibrary\_39389535\_81975228.PDF.

2. Olifer V.G., Olifer N.A. Komp'yuternye seti. Principy, texnologii, protokoly: Uchebnik dlya vuzov. [Computer Networks: Principles, Technologies, Protocols. Textbook for Higher Education Institutions]. 3-e izd. SPb: Piter, 2008. 958 p.

3. Mikushin A.V., Sazhnev A.M., Sedinin V.I. Cifrovye ustroystva i mikroprocessory. [Digital Devices and Microprocessors]. SPb: BXV-Peterburg, 2010. 832 p.

4. Shilo V.L. Populyarnye cifrovye mikrosxemy. [Popular Digital Microcircuits]. M.: Radio i svyaz', 1987. 352 p.

5. Ue'jkerli Dzh. F. Proektirovanie cifrovych ustroystv. [Designing Digital Devices]. M.: Postmarket, 2002. 544 p.

6. Novikov Yu.V. Osnovy cifrovoj sxemotexniki. Bazovy'e elementy i sxemy. [Fundamentals of Digital Circuit Engineering: Basic Elements and Circuits]. Metody proektirovaniya. M.: Mir, 2001. 379 p.

7. Ugryumov E.P. Cifrovaya sxemotexnika. [Digital Circuit Engineering]. SPb: BXV-Peterburg, 2004. 528 p.

8. Bukreev I.I., Goryachev V.I., Mansurov B.M. Mikroe'lektronny'e sxemy' cifrovyyx ustrojstv. [Microelectronic Circuits of Digital Devices]. M.: Texnosfera, 2009. 714 p.

9. Bryakin L.A. E'lektrotexnika i e'lektronika: Konspekt lekcij. [Electrical Engineering and Electronics: Lecture Notes]. Penza: Izd-vo PGU, 2004. 152 p.

**Дата поступления: 20.12.2025**

**Дата публикации: 20.02.2026**